FPGA ROM

2020506 张胜

通过完成一个个具体的任务来逐步掌握精通 FPGA,成为一个设计的手段和武器。

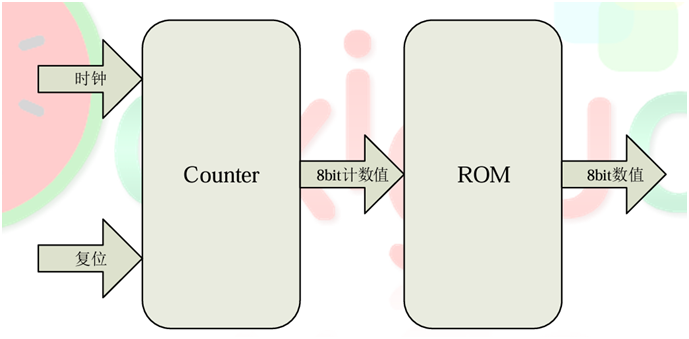

这里用到了计数器和ROM 两个模块 。在TOP程序中如何用代码组织起来。没有任何诀窍,就是把代码读熟,把实物和代码对上号。

module rom_top(clk,reset_n,rom_data);

input clk;

input reset_n;

output rom_data;

wire [7:0] counter_out;

counter counter_1(

.clk (clk) ,

.reset_n (reset_n),

.counter_out (counter_out)

);

rom rom_1 (

.address (conunert_out),

.clock (clk),

.q (rom_data)

) ;

endmodule

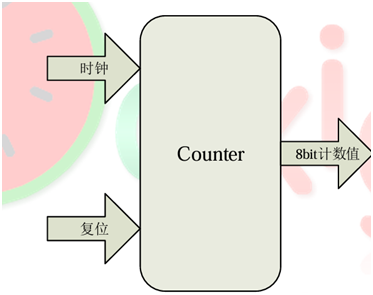

counter 模块

module counter(

clk,

reset_n,

counter_out

);

input clk;

input reset_n;

output [7:0]counter_out;

reg [7:0]counter_reg;

assign counter_out = counter_reg;

always @(posedge clk or negedge reset_n)

begin

if(reset_n == 1’b0)

begin

counter_reg <= 8’d0;

end

else

begin

counter_reg <= counter_reg + 1’b1;

end

end

endmodule

rom 模块 自动生成的

// synopsys translate_off

`timescale 1 ps / 1 ps

// synopsys translate_on

module rom (

address,

clock,

q);

input [7:0] address;

input clock;

output [7:0] q;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_off

`endif

tri1 clock;

`ifndef ALTERA_RESERVED_QIS

// synopsys translate_on

`endif

wire [7:0] sub_wire0;

wire [7:0] q = sub_wire0[7:0];

altsyncram altsyncram_component (

.address_a (address),

.clock0 (clock),

.q_a (sub_wire0),

.aclr0 (1’b0),

.aclr1 (1’b0),

.address_b (1’b1),

.addressstall_a (1’b0),

.addressstall_b (1’b0),

.byteena_a (1’b1),

.byteena_b (1’b1),

.clock1 (1’b1),

.clocken0 (1’b1),

.clocken1 (1’b1),

.clocken2 (1’b1),

.clocken3 (1’b1),

.data_a ({8{1’b1}}),

.data_b (1’b1),

.eccstatus (),

.q_b (),

.rden_a (1’b1),

.rden_b (1’b1),

.wren_a (1’b0),

.wren_b (1’b0));

defparam

altsyncram_component.address_aclr_a = “NONE”,

altsyncram_component.clock_enable_input_a = “BYPASS”,

altsyncram_component.clock_enable_output_a = “BYPASS”,

altsyncram_component.init_file = “sin.mif”,

altsyncram_component.intended_device_family = “Cyclone IV E”,

altsyncram_component.lpm_hint = “ENABLE_RUNTIME_MOD=NO”,

altsyncram_component.lpm_type = “altsyncram”,

altsyncram_component.numwords_a = 256,

altsyncram_component.operation_mode = “ROM”,

altsyncram_component.outdata_aclr_a = “NONE”,

altsyncram_component.outdata_reg_a = “CLOCK0”,

altsyncram_component.widthad_a = 8,

altsyncram_component.width_a = 8,

altsyncram_component.width_byteena_a = 1;

endmodulerom 模块

コメント